誰能替代銅互連?

隨著臨界互連尺寸接近10nm,目前銅「雙大馬士革」也變得越來越具有挑戰性,替代金屬化方案的研究力度在大約十年內不斷加強。選擇替代金屬是一項高度多方面的任務,包括許多標準,包括降低尺寸時的電阻率、可靠性和性能方面,以及可持續性方面。

在本文章中,我們介紹了替代金屬基準測試和選擇的基本標準,並討論了該領域的當前技術狀況。本教程內容包括接近製造的材料介紹、實際研究中的材料以及基礎研究的未來方向。雖然商用CMOS器件中銅金屬化的第一種替代品最近已成為現實,但對這種終極互連金屬的研究仍在進行中。

一、介紹

微電子電路是當今生活中幾乎每一個方面的無數電子設備的核心元件。邏輯電路、存儲單元和傳感器不僅用於計算機或手機中,而且用於汽車或醫療應用中來處理、存儲和檢測信息。 微電子學的成功依賴於底層構件的不斷小型化,在基於晶體管的邏輯電路中,著名的摩亞定律就是這一點的縮影。等效縮放定律也存在於其他器件中,例如存儲單元。器件尺寸的減小與器件密度的巨大增加相結合,帶來了巨大的性能優勢,同時也降低了能耗,並且至少對於老一代來說,每個功能的成本大大降低。例如,從1970年到今天,製造一個晶體管的成本降低了109倍。

在公眾的認知中,晶體管或電容器單元的縮放曆來是焦點。然而,互連的縮放對於支持摩亞定律是同樣重要的。互連線和通孔為電路的有源元件(如互補金屬氧化物半導體(CMOS)晶體管或存儲元件)提供信號、電源和時鍾,因此在創建具有高級功能的複雜微電子電路和系統時至關重要(圖1a)。

作為示例,在邏輯處理器中用作高速緩存存儲器的SRAM單元的區域在一個方向上由晶體管的柵極間距(也稱為「接觸多晶矽間距」)(晶體管尺寸)和垂直方向上的金屬線的間距(互連間距)確定(圖1b)。因此,為了減小SRAM單元面積,晶體管和互連尺寸兩者都應當被縮放。

從歷史上看,當尺寸減小時,晶體管性能得到改善,從而帶來上述性能優勢。相比之下,這並不適用於互連。減小導線的橫截面積必然會增加其每單位長度的電阻,從而導致更大的能量耗散和增加的RC延遲。如今,在12nm至15nm量級的互連線尺寸下(參見第1A),互連性能通常是先進微電子電路整體性能的主要限制因素。對於晶體管來說,器件結構的變化伴隨著互連線的改進。

然而,對於互連線來說,結構的選擇是有限的,因此,必須通過材料和工藝創新來提高性能。通過使用具有較低介電常數(低-κ ε)的電容器或空氣間隙可以實現互連電容的減小。然而,由於所得互連的機械穩定性降低,這導致封裝期間的可靠性問題,從而其進展受到阻礙。

1999年以後,取代鋁基金屬化的銅「雙大馬士革」方案(圖2)由於多種原因正面臨著日益嚴重的問題。

首先,銅需要擴散阻擋層和粘附襯墊以確保互連可靠性。如果沒有擴散阻擋層(通常為TaN基),銅漂移到周圍的電介質中會導致快速的電介質擊穿和相鄰線路之間的短路(參見第三章)。

此外,在縮放尺寸下,銅電遷移成為日益嚴重的問題(參見第三章)。這可以通過在TaN阻擋層和銅之間的粘附襯墊層(通常為Co)以及通過覆蓋層來減輕。然而,阻擋層和襯墊層的厚度不能在不喪失其功能的情況下按比例縮小到2-3nm量級的組合厚度。因此,對於具有減小寬度的線,阻擋層和襯墊層(具有高電阻率)佔據總的金屬化的體積分數越來越大,為銅留下越來越少的空間,而對線的電導率幾乎沒有貢獻。

再者,如下面將要討論的,由於晶界和表面散射的增加的影響,銅的電阻率對於縮放的尺寸強烈增加。這兩種效應——更高的電阻率和減少的Cu體積分數——都有助於在互連縮小時,單位長度的線路和通孔電阻迅速增加。這導致互連性能的迅速惡化,即使對於短的線也是如此。

最後,「雙大馬士革」製造方案需要逐步進行破壞性修改,以實現具有高機械穩定性的無空隙和無缺陷互連。

這些問題可以通過選擇理想情況下不需要阻擋層和襯墊層的替代金屬來緩解,同時對小尺寸電阻率的敏感性較弱。雖然這不能逆轉單位長度線路電阻的增加,但我們將在下文中證明,在足夠小的線寬下,替代金屬和金屬化方案的性能優於銅。

在本文中,我們將介紹與選擇潛在的替代金屬用於高級互連相關的不同方面。甄選過程是多方面的,需要解決許多方面的問題。因此,我們開發了一個多階段的過程,以識別、篩選和基準測試互連應用的替代金屬(圖3)。教程的組織結構如下:

我們將首先討論電阻率對納米尺寸的敏感性,並介紹材料篩選過程。隨後將引入可靠性(TDDB)和電遷移(EM)。本論文還介紹了這一方法在元素、二元和三元金屬中的應用,並討論了目前和未來的研究方向。由於金屬選擇與未來集成方案之間存在密切關係,我們將在未來技術節點中解決替代金屬的集成和工藝問題。

最後,可持續性集成電路對於減少微電子產業的生態足跡正變得越來越重要。因此,我們將引入互連金屬的生命週期評估方案,並將其應用於基於上述標準確定的各種有前景的金屬。

未來互連技術目標

從歷史上看,互連尺寸的縮放一直由行業範圍的路線圖驅動,例如半導體的國際技術路線圖(ITRS),目前稱為國際器件和系統的路線圖(ITRDS)。然而,目前還不存在行業範圍的路線圖,並且技術節點命名法也變得模糊不清。目前,商用先進微電子芯片中的最小互連間距在表1的順序排列,邏輯電路中互連尺寸(最小金屬間距)的路線圖。改編自參考文獻。有關當前技術水平,請參見參考文獻和(HVM =大批量製造; GAA =全方位柵極; CFET =互補場效應晶體管)。

表1

表125納米,在未來十年內預計將進一步減少(見表1),在不久的將來達到低於10nm的預測線寬。這是特別重要的,因為接觸的多晶矽間距(晶體管柵極間距)不能進一步小型化。 因此,未來的重要領域收益,例如SRAM單元,需要主要來自晶體管架構以及互連間距縮放。

如上所述,如此小的線寬可能與當今互連中使用的銅「雙大馬士革」(圖2)不兼容。雖然銅「雙大馬士革」的進一步優化仍在進行中,但表1中路線圖中的最小互連尺寸將需要使用潛在的新材料,工藝以及集成方案的顛覆性方法。如表所示,互連線和通孔的相關尺寸將在約5和10 nm之間的範圍內,這可以用作金屬選擇以及工藝開發的指導。

二、納米尺度的金屬電阻率

幾十年來已經知道,金屬納米結構(例如薄膜或納米線)的電阻率通常比相應的大塊金屬電阻率高得多。

這是互連縮放的主要問題,因為這導致線和通孔電阻的增基比單獨減小幾何尺寸所預期的要快得多,特別是在低於10nm的目標尺寸範圍內。電阻率的增加歸因於粗糙表面或界面以及晶界處散射的綜合效應。為了定量描述,對於具有頂和底表面/界面的薄膜,已經發展了各種傳遞模型。然而我們注意到,目前還沒有一個等效的一維傳遞模型可以描述具有四個環繞表面的導線。然而,基本的定性行為預計是相當類似的,因此「薄膜衍生」電阻率模型已被用來瞭解納米線的縮放性能。

體金屬和納米結構中的電子傳遞

1. 電子傳遞的半經典描述

瞭解低維電阻率增加的最常用方法是基於玻爾茲曼輸運方程(BTE:Boltzmann Transport Equation)。BTE描述了載流子分佈不平衡的統計,例如,當施加電場時,該電場的強度會隨時間而變化。

此部分有諸多公式,放原文方便大家理解

此部分有諸多公式,放原文方便大家理解如前所述,Eq(7)的推導假設聲子和晶界散射的Matthiessen規則是有效的。對於無序度較大的納米晶近非晶薄膜,可能違反了Matthiessen規則。在這種薄膜中,局部化效應變得很重要,這通常伴隨著相對於體行為的顯著降低的溫度依賴性(電阻率的溫度係數)。

然而,Eq(7)的推導並不要求對錶面散射、晶界散射或聲子散射都成立Matthiessen規則。事實上,由於晶界散射對平均自由程的「重整化」,在Ref中已經指出,對於金屬薄膜中的表面散射和晶界散射,Matthiessen規則通常不成立。這使得單獨量化體積、表面散射和晶界散射對薄膜電阻率的貢獻變得困難,並且應該謹慎使用公式(7)的某些近似版本,將表面和晶界散射的貢獻分開。

2. 薄膜電阻率縮放的材料依賴性

Eq(7)包含了該問題的五個獨立材料參數:體單晶電導率、電子平均自由程、薄膜表面/界面處散射的鏡面度、平均晶粒尺寸和晶粒反射係數。在實踐中,人們經常發現的晶粒尺寸對膜厚的強烈依賴性,這導致了第二個間接的源的厚度依賴性的薄膜電阻率,除了表面散射。 晶粒尺寸和膜厚之間的關係ℓ(h)強烈地依賴於沉積工藝參數,並且不是材料本身的唯一函數。 雖然有時假定線性關係,但在相關厚度範圍內,通常在實驗上觀察不到這種關係(見圖4a)。 它也可能受到沉積後退火的影響,這可能導致晶粒生長或再結晶。

因此,僅根據體性質定量預測金屬納米結構的電阻率是不可能的。如前所述,ℓ(h)的關係取決於沉積過程特徵和熱收支;由於實驗表明晶界散射可以主導薄膜的電阻率,因此金屬的篩選應包括獲得大晶粒薄膜(或納米線)的可能性。然而,這不能通過(從頭算)計算來實現,因此,晶粒尺寸和退火行為的實驗研究需要補充傳輸和可靠性代理,以實現更現實的金屬評估。

第二個限制是難以計算或預測參數R和p的實際值。R描述了電子在晶界的反射概率,它通常取決於晶界兩側晶粒的(相對)取向和晶界的原子構型。一般來說,計算和實驗一致地觀察到小角度或巧合晶界(低R)與大角度隨機晶界(大R)之間的R有很大差異。在多晶薄膜中,相關R將是所有晶界構型的有效平均值,因此取決於微觀結構。雖然某些具有內聚能的趨勢——更大的內聚能有望導致更大的R——似乎是合理的,但R不能被認為只取決於金屬。

此外,表面散射鏡面率p不僅與金屬本身有關,還與周圍界面或表面的性質有關。預計包層材料和界面或表面粗糙度都將起主要作用。雖然從理論上和實驗上研究了表面散射率作為表面粗糙度的函數,但理論和實驗之間的定量一致尚未建立。因此,計算不能預測,不能用於篩選。此外,由於對包層材料和表面粗糙度的潛在依賴,表面散射不能被認為是一種材料性質。

然而,上一節表明,由於表面或晶界散射,電阻率的增加與載流子的整體平均自由程λ成比例。因此,大R、小晶粒或擴散界面的影響可以通過短λ來減輕。如圖4b所示,以ρ0 = 5.3µΩcm, R = 0.45, p = 0(漫射表面散射),固定厚度為20 nm為例,用Eq.(7)計算薄膜電阻率與晶粒尺寸的關係。

結果表明,較短的平均自由程λ使得電阻率對晶粒尺寸的依賴性較弱,從而減輕了晶界散射的影響。在擴散表面散射的情況下,薄膜電阻率隨薄膜厚度的變化也有類似的規律。因此,這導致了尋找具有短λ的金屬作為Cu的替代品。Cu的平均自由程可以達到高達40nm的值,這與典型的互連尺寸和晶粒尺寸相比是很大的。

因此,平均長度短得多的金屬對互連結垢的敏感性要低得多。一種基於ab-initio的篩選短λ金屬的方法將在第IIC節中描述。完整的替代金屬篩選過程,包括其目前的狀況將在第四節中詳細說明。

3. 各向異性對薄膜電阻率縮放的影響

上述模型假設一球面各向同性費米表面(具有有效質量的自由電子氣體),因此體電阻率和薄膜電阻率都不依賴於電流的結晶方向。這樣就可以推導出Fuchs-Sondheimer Eq.(5)和Mayadas-Shatzkes Eq.(7)。由於複雜性大,目前還沒有薄膜電阻率模型能夠結合表面和晶界散射考慮金屬的詳細能帶結構。雖然Mayadas-Shatzkes模型(Eq.(7))已經能夠很好地描述實驗測量,但缺少對模型參數R和p的定量理解限制了對不同金屬的球面費米表面近似精度的評估。

應該注意的是,從宏觀的角度來看,立方系統的電導率是各向同性的,因此,用球面費米面近似可能是合適的。然而,其他不對稱的(六角形、四角形、正交形、單斜形、三角形)結構會導致大塊金屬的各向異性電導率。

以六角形釕為例,其沿六角形軸的電阻率低於兩個垂直(平面內)方向。為了描述這種情況,我們建立了一個半經典的mayadas – shatzkes模型來描述脂質費米曲面。這種模型可以表示具有六角形、四角形或正交晶體對稱的金屬,數學細節超出了本教程的範圍,但該模型發現費米表面各向異性對錶面散射有很強的影響,而不影響晶界散射。圖5顯示了使用參考文獻中的模型,體電阻率與薄膜的關係是費米表面有效質量各向異性的函數。這裏忽略了晶界散射(R = 0),只有表面散射是有效的。

結果表明,對於面內電導率大(面內有效質量小)、面外電導率小(面內有效質量大)的二維金屬,表面散射逐漸被抑制,同時由於表面散射導致的薄膜電阻率對厚度的依賴性降低。

原則上,這種效應可以用來降低納米線的電阻率,因此,已經提出了二維和一維金屬(具有單一高導電性晶體地理方向)用於互連應用。然而,有兩點值得注意。由於Matthiessen規則一般不適用,因此存在強晶界散射(不受降維影響)導致二維金屬的表面散射受到抑制,從而降低了小晶粒金屬因各向異性而具有的優勢。此外,在互連中使用一維金屬需要單晶金屬,以便電流方向始終與高導電性的晶體方向對齊。目前,在商業互連中沒有可行的單晶線集成路線,因此,這種考慮目前僅限於基礎材料科學。

金屬中的點缺陷、無序和合金散射

在介紹基於平均自由程λ的第一性原理篩選方法來識別和選擇有前途的互連應用金屬之前,我們簡要介紹了對復合金屬非常重要的其他散射源。

一般來說,晶體中任何偏離週期性的地方都會使電子散射。元素金屬含有空位(或空位團簇)缺陷或雜質。在相關金屬的典型多晶高質量薄膜中,空位和雜質限制了低溫下的電阻率,但在室溫下通常可以忽略不計,在室溫下,聲子、晶界和表面的散射佔主導地位。

然而,對於復合金屬來說,情況就大不相同了。合金是一種本質上無序的材料,其晶格上不同原子的分佈是隨機的。由此產生的晶體因此不是週期性的,由於合金散射導致高電阻率。這在圖6中說明了Cu-Au系統的開創性情況。無序無序CuxAu1−x合金的電阻率遠大於單質金屬Cu和Au,在Au的50%處電阻率最大,無序程度最大。相比之下,該體系還包含兩種有序的金屬間相:Cu3Au和CuAu。接近這些有序相的化學計量,電阻率顯示出一個明顯的最小值,遠低於無序無序合金。

這些觀察結果表明,為了實現與互連應用相關的復合金屬的電阻率,需要避免合金散射。因此,除了不會引起這些問題的元素金屬外,只有有序的金屬間化合物對替代金屬篩選工作具有潛在的興趣。測量和優化薄膜金屬間有序的挑戰加劇了這一問題。更多的細節和技術狀況的總結可以在Secs中找到。IVC和IVD。

替代金屬的初始篩選

如果不詳細瞭解微觀結構,就不可能預測薄膜或納米線的電阻率,而微觀結構與工藝有關。此外,像Eq.(7)這樣的電阻率模型假設一球形費米表面(自由電子氣體),並且金屬特有的標度特性僅由單個平均自由程值表示。雖然可以根據第一性原理計算金屬的電子-聲子限制電阻率,但考慮到詳細的能帶結構,這在今天的計算中仍然非常密集,將實際系統的大小限制在每個單元電池的幾個原子。主要的瓶頸是電子-聲子耦合弛豫時間的計算。

此外,用這種形式包括晶界是很麻煩的。所有這些問題都限制了建立完全預測下選擇方法的可能性,這種方法可以立即確定直接互連應用中最有前途的金屬候選材料。因此,金屬選擇問題需要分階段解決,如圖3所示。儘管如此,通過所謂的ρ0λ值可以篩選潛在感興趣的金屬,該值可以用有限的計算努力通過從頭算方法計算。在下面第四節中將描述篩選元素和化合物金屬的總體方法的應用。

此部分有諸多公式,放原文方便大家理解

此部分有諸多公式,放原文方便大家理解存在表面散射的薄膜和納米線的電阻率縮放

雖然它已成功地應用於篩選元素和化合物金屬,上述方法是近似的。在實際中,載流子的平均自由程在很大程度上取決於它們的波矢量k。如圖7所示,Cu的平均自由程沿費米面方向分佈廣泛。因此,重要的是在輸運計算中包括全各向異性帶結構以及篩選工作,以獲得更準確的小尺寸電阻率圖像。

方程(4)描述了包括所有相關散射機制在內的體弛豫時間的重新標度。請注意,晶界散射原則上包括在(有效)平均自由程中。假設一球面費米曲面可以得到方程7中描述的解析Mayadas Shatzkes模型。包括完整的電子能帶結構會導致:

其中τ0nk為包括聲子和晶界散射的弛豫時間。當忽略後一種散射事件(即僅包括聲子和表面散射)時,薄膜電阻率可以從頭開始預測。Cu的計算薄膜電阻率隨薄膜厚度的變化如圖7所示。注意,Eq. 12表明,薄膜(或納米線)的電阻率不僅取決於輸運方向,還取決於表面法向(生長方向)。

這甚至適用於具有各向同性體積導電性的金屬,例如包括Cu在內的所有立方金屬,並且可以通過減小尺寸的對稱性來理解。

對於具有可忽略晶界散射的單晶薄膜,儘管採用通常的密度泛函理論近似,但結果原則上是準確的。原則上,紋理薄膜中的晶界散射可以通過晶粒尺寸相關的平均自由程來增加,但這取決於微觀結構,並且不容易通過最先進的從頭算技術來解決。

除了輸運計算之外,上述模型還可用於推導薄膜或納米線的優值,相當於Eq.10的ρλ。例如,對於納米線,這會導致:

這個性能值包括各向異性輸運的影響,例如第IIA1節中討論的表面散射的抑制,適用於有織構的單晶線,尤其是單晶線。對於某些晶體取向的材料,它可以產生非常有吸引力的價值。然而,值得注意的是,隨機多晶薄膜和電線是用平均方法表徵的,表面散射是在所有晶粒方向上平均的。此外,對於以晶界散射為主的薄膜或納米線(如小晶粒多晶薄膜),對生長取向的依賴程度降低。在這種情況下,使用10對金屬進行基準測試是最合適的。

三、互連可靠性

選擇新的互連金屬化方案的第二個重要方面是金屬和介電的可靠性。互連故障可能由於金屬或電介質故障而發生。與線路電阻類似,當導線和過孔小型化時,互連的可靠性往往會降低。最初,Al有限的電遷移性能導致了20多年前Cu作為主要互連金屬化的引入。目前,銅金屬化的可靠性面臨著越來越大的壓力。正如下面更詳細解釋的那樣,為了確保可靠性,需要屏障層和襯墊層,但它們需要與互連尺寸一起縮小,以便為Cu導體留出一些空間。由於其可擴展性有限,屏障和襯管最終將佔據互連體積的很大一部分,而對整體電導的貢獻很小。正如將在第五節中所示,壘和無襯裡金屬化對於低電阻互連至關重要,優於當前的銅金屬化方案。

下面,我們將介紹電介質和金屬可靠性的基本原理。第四節將介紹特定元素和二元替代金屬可靠性的最新技術狀況。

介電擊穿和阻擋層的需要

隨時間變化的介電擊穿 (TDDB:Time-dependent dielectric breakdown ) 是一個物理過程,其中介電材料在低於其固有擊穿強度的恒定電場下會隨著時間的推移而降解並最終擊穿。這是由於電介質中形成導電路徑(細絲),使相鄰金屬電極短路。快速失效可能是由逐漸的介電損壞引起的(例如,空位形成)或通過相鄰電極(此處為互連線或通孔)的金屬漂移。在後一種情況下,由於施加的電場,金屬離子漂移穿過電介質,汙染電介質,導致泄漏,並最終導致電介質擊穿和互連線短路。

TDDB 行為很大程度上取決於所使用的材料,包括金屬和電介質。對於金屬,存在熱力學勢壘,用於(電離)金屬原子的分離及其漂移或擴散到(低-K)電介質。一般來說,這種勢壘與金屬的內聚能成比例。因此,對於難熔金屬,該勢壘明顯高於銅,從而抑制金屬離子向電介質中的漂移和擴散,從而獲得更長的 TDDB 壽命。我們注意到金屬離子的漂移和擴散 裡面 電介質對金屬內聚能的依賴性明顯較小,而是取決於電介質中金屬雜質的結合能。然而,對於與互連相關的金屬,熱力學勢壘由分離能給出,因此具有更高內聚能的金屬(更難熔的金屬)預計將表現出大大改善的 TDDB 壽命。

另一方面,電介質的選擇也會影響互連的 TDDB 性能。當今先進互連中使用的電介質具有低介電常數(低介電常數K)以減少互連電容。低介電常數 K 這些電介質的連接由於低偶極子密度,或者本質上是由於成分或通過降低物理密度, 例如,通過引入孔隙率。這會對 TDDB 行為產生相當大的影響,因為眾所周知,銅在此類電介質中會快速分離和漂移,從而導致快速擊穿。

因此,銅需要在電介質和銅金屬化之間引入(更難熔的)阻擋層,以阻止銅脫離和漂移到電介質中。一般來說,非晶勢壘金屬優於多晶勢壘金屬,因為晶界可以充當擴散路徑。

如今,阻擋層由 TaN 製成,其厚度可以縮小到約 1 至 1.5 nm,而不會損失功能。替代阻隔材料的研究仍在進行中, 例如,在摻雜 Zn 的 Ru 上,但它們的集成通常並不簡單,預計它們不會比 TaN 屏障有大的改進。

除了固有的材料特性之外,工藝限制和尺寸縮放本身也會進一步降低 TDDB 性能:窄間隙、線邊緣粗糙度、等離子體損傷或未對準(見圖 1)。因此,為先進互連尋找合適的替代金屬原則上不僅應基於其固有性能(固有金屬分離勢壘),而且還應基於對其集成步驟的影響,因為在先進互連中實施新材料可能會導致增強的介電擊穿。

因此,使用合適的測試結構(例如平面電容器 (PCAPS))通過實驗評估 TDDB 性能非常重要或側壁電容器(SWCAPS),122 用於向下選擇有前途的替代金屬。

TDDB 的主要驅動力是施加的電場以及互連的溫度。實際上,TDDB 限制了相鄰線路之間可以安全施加的最大電場,因此對於電路設計和佈局非常重要。商業電路的 TDDB 壽命規格在高達 135 的溫度下通常為 10 年. 這樣的壽命太長而無法直接測量,因此必須通過外推加速測量來提取可靠運行的最大電場。 在高溫和電場下。在文獻中,關於使用哪種模型進行 TDDB 壽命外推一直存在爭論,並且已經提出了幾種模型,例如:

圖8. 說明對 TDDB 和互連壽命的不同影響: 1) 電介質的固有特性、擊穿位置和機制; 2)絕緣介質的厚度; 3)阻隔性能和導體金屬脫離; 4)集成引起的介電損傷, 例如、阻擋層沉積、化學機械拋光、蝕刻、吸濕、 ETC。); 5) 線路變異性(線路邊緣粗糙度、溝槽高度、通孔未對準、 ETC)。

圖9. TDDB 壽命外推可用模型的比較 與 使用 TDDB 數據進行測量。

圖9. TDDB 壽命外推可用模型的比較 與 使用 TDDB 數據進行測量。

這裏, t50% 指示時間,在此之後線路以 50% 的概率出現故障。衝擊損傷模型(幸運電子模型)被認為最能描述TDDB的底層物理機制。然而,一些作者更喜歡使用冪律模型來擬合 TDDB 數據,因為它提供了良好的預測並且具有有限數量的擬合參數。123,125,126 相比之下,鑲嵌結構的研究已經發現E- 和 √E-模型也是如此,在擬合低場 TDDB 數據時保守。不同模型的行為以及與 Cu 實驗 TDDB 數據的比較如圖 9 所示。請注意,需要額外的面積縮放和外推至低故障百分位,以獲得行業相關互連的故障率和操作條件限制。

加速TDDB測試還可以用於研究底層機制,例如,擊穿是通過介電失效還是通過金屬絲形成發生。典型的偏置溫度應力 (BTS) 實驗在高溫下使用 PCAP 或 SWCAP,例如, 通過三角電壓掃瞄 (TVS) 或施加恒定電壓(見圖10)。對於具有不同電極(一個是感興趣的金屬,另一個是難熔金屬)的電容器,可以通過研究正偏壓和負偏壓下的擊穿來證明金屬漂移(並與本征擊穿區分開來)。在「弱」頂部電極上施加正電壓應力期間, 例如,PCAP(圖10a),在沒有合適的擴散勢壘的情況下,金屬離子漂移到電介質中(圖10b),而負電壓應力不會發生金屬漂移(圖10C)。這允許金屬漂移和其他固有電介質擊穿機制的分離,因為後者不依賴於偏置極性(參見圖10d 和 e)。

或者,在三角電壓掃瞄期間,當漏電流在第一次電壓掃瞄期間增加但在後續掃瞄期間消失時,可以檢測到金屬漂移,這表明金屬離子已遷移通過電介質(見圖10f-i)。這種 TDDB 測量可以在各種溫度和電壓下進行,以研究與本征擊穿、金屬細絲生長和細絲形成相關的各種條件。由於這些機制的主導地位是由金屬、介電材料及其厚度決定的,因此有必要不斷修改替代金屬和先進互連的方法。

從 TDDB 的角度來看,Cu 互連縮放的關鍵限制是需要阻擋層來防止導體金屬脫離和漂移到周圍的電介質中。在按比例縮放的互連中,互連尺寸減小,此類勢壘具有比銅高得多的電阻,並且由於線寬的縮放,佔據了互連線體積的很大一部分,並最終阻礙了超小線寬的適當金屬填充。正如第五章中進一步討論的那樣。這會導致線寬低於 10 nm 的縮放互連的線電阻大幅增加,並最終強製引入無障礙替代金屬化。

圖 10. (a) 用於確定 TDDB 壽命的平面電容器 (PCAP) 的器件結構。(b) 和 (c) 恒壓應力下的金屬漂移過程示意圖。對於 “弱 “金屬頂電極,在正電壓下金屬離子會漂移,而在負偏壓下不會發生金屬漂移。(d)和(e)顯示了相應的失效時間(湯臣F)行為與施加偏置電壓 ±V 的函數關係。(f)至(i)顯示了在三角形電壓掃瞄過程中金屬絲的形成和溶解,外加電場 E 如圖所示。

電遷移

眾所周知,電遷移 (EM:Electromigration) 是集成電路 (IC) 中的主要故障機制之一。當電流流過導體時,金屬原子受到兩種力:電場產生的直接力和移動電子的動量轉移(或電子風)產生的力(圖 11a)。

隨著時間的推移,電子風會導致金屬原子沿著電子流的方向從陰極遷移到陽極。結果,陰極側會出現金屬原子耗盡,從而形成空隙(圖11b 和 c)並最終導致線路開路。

同樣,金屬原子將聚集在陽極一側,促進小丘的形成(圖 11b),並最終導致短路。

描述電磁過程的驅動力 FEM(也稱為電子風力 Fwind)134 可表示為:

其中 ρ 為金屬電阻率,je 為電子電流密度,Z∗ 為有效離子價,e 為電子電荷。

愛恩斯坦方程將原子質量通量 J 與電子風聯繫起來:

其中,C 為原子濃度,D 為擴散常數 D = D0 exp – EA kBT,D0 為沿不同路徑的有效擴散係數,EA 為主要擴散路徑的活化能,kB 為玻爾茲曼常數,T 為溫度。

在金屬線中,原子可以沿著幾條路徑擴散:在金屬線的主體中、沿著晶界以及在金屬和電介質的界面上。主要的擴散路徑與材料有關,由其活化能 EA 決定,而活化能 EA 又由晶體金屬晶格的鍵能決定。在銅互連中,電磁導致的空洞通常在銅和介質屏障(通常為 SiN 或 SiCN)之間的頂部界面成核,空洞的生長將通過晶界繼續進行。

縮小互連尺寸的影響之一是界面和晶界處擴散原子的體積迅速增大,同時金屬體積減小。因此,按比例互聯中能夠可靠承載的最大電流密度(135◦C 下的壽命為 10 年)會降低,從而導致電路設計和佈局受到越來越嚴格的限制。通過在 TaN 層和導體之間引入襯墊層,特別是在線路頂部引入襯墊層,按比例互連中電磁壽命的縮短得到了緩解(減緩)。

目前使用的主要襯層材料是 Co,Ru 也是一種替代材料。然而,與防止銅漂移到周圍電介質的 TaN 阻擋層類似,襯墊層的厚度也很難調整。預填充技術可能是一種替代方法,可提高可靠性,但會增加工藝複雜性。這就減少了主導體金屬(即銅)的空間,當尺寸縮小時,線路電阻會迅速增加。

替代襯墊縮放的另一種方法是使用其他導體金屬,這些金屬對電磁具有較大的三相電阻,大大優於銅。由於電磁的活化能 EA 通常與金屬的內聚能成正比,因此熔化溫度高的難熔金屬很有前途。我們注意到,這類具有高內聚能的金屬在無障礙 TDDB 可靠性方面也很有前景,這表明不同可靠性方面的材料依賴性是相關的。第五節將進一步討論選擇對無屏障和無襯墊可靠金屬化方案具有良好前景的替代金屬的重要性。

自熱和熱特性

如上所述,金屬互連的可靠性主要取決於芯片中互連結構臨界點的 ab 溶質溫度以及金屬堆棧中的溫度梯度。互聯結構中達到的溫度取決於互聯結構的熱阻、互聯結構與發熱晶體管之間的熱耦合、互聯結構中的自加熱以及金屬線之間的熱耦合。

金屬互連尺寸的不斷擴大,加上低介電常數介電材料的引入,導致人們對互連溫度越來越關注。由於層間電介質的熱傳導率通常很低,例如 OSG 3.0(一種介電常數為 κ = 3.0 的有機矽玻璃)的熱傳導率為 0.3 W(m K)-1通過互連堆棧的熱傳導主要是通過金屬線和通孔進行的,並且在很大程度上取決於金屬傳導率和金屬連接方案。減少金屬線的寬度和厚度會降低熱導率,增加電阻率(見第二章),這導致互連堆棧的熱阻增大,成為先進封裝整體熱阻的主要因素,並導致金屬互連的自熱升高。

由於互連結構的熱行為由金屬主導,因此準確預測替代金屬的熱特性非常重要。互連級熱模型148,149 可以包括金屬線密度、通孔密度和不同金屬層之間連接性的影響,但還需要包括有關尺寸相關行為的額外信息。

為了捕捉包括電子和聲子在內的彈道熱傳導效應,可以使用 ab initio 模擬來預測材料的熱導率。塊狀金屬的總熱導率是根據所有電子和聲子模式的累積貢獻計算得出的,即:

其中 C 是熱容量,v 是群速度,τ 是弛豫時間。下標 el 和 ph 分別表示電子和聲子的貢獻,k 和 q 分別表示電子和聲子的波函數。在半導體材料中,聲子主導熱傳導,而電子是金屬的主要熱載體。因此,對於金屬而言,導熱係數 K0 和電阻率 ρ0 通過韋迪曼-科蘭茨定律聯繫在一起:

L 為洛倫茲數,T 為溫度。對於自由電子,L = 2.4 × 10-8 WΩK-2。許多塊狀金屬的洛倫茲數接近自由電子值(如 Cu150),但鉑族金屬151 或 W150 的洛倫茲數要高出 10-15% 左右,這是因為聲子傳輸對熱導率的影響。

為了將金屬尺寸減小對熱導率的影響考慮在內,我們採用了基於 Mayadas 和 Shatzkes 模型(見第 II 章 A 1 節)的薄膜模型,利用反射係數和表面鏡面參數的經驗心理校準數據(另見第 IV 章),得出了不同金屬(疊層)的熱導率隨尺寸變化的估計值。

根據這一模型,可以得出聲子和電子對總熱導率的貢獻。圖 12a 顯示,在先進互連結構的相關尺寸中,聲子的貢獻率仍遠低於 15%,這表明熱傳導端口由電子主導,且維德曼-弗朗茨定律仍(近似)適用。圖 12b 顯示了幾種金屬隨厚度變化的熱導率。熱導率與尺寸相關的行為受到電子平均自由路徑以及晶界和表面散射特性的影響。雖然理論和實驗表明洛倫茲數可能會降低,但對於納米級尺寸的金屬膜和金屬絲而言,洛倫茲數是否會發生強烈變化仍是一個未決問題。

圖 12. 隨厚度變化的熱導率趨勢:(a)聲子傳輸對總熱導率的貢獻。(b) 與厚度有關的總熱導率,包括聲子和作為熱載體的電子。

四、向下選擇替代金屬

由於製造接近目標尺寸的納米級線路既複雜又昂貴,而且在許多情況下由於缺乏工藝技術而無法實現,因此在潛在的大量候選金屬中直接通過實驗識別出最有利的金屬是不可行的。因此,最初必須設計一種程序,根據可從多種材料中獲得的代用指標來識別和篩選最有前途的金屬。很明顯,這套代用指標並不是獨一無二的,曆來採用的方法也略有不同,但如上所述,它應涵蓋納米級金屬電阻率和可靠性。然後,可以通過薄膜實驗等方法進一步瞭解候選金屬的特性,並按照圖 3 中的工作流程,將其作為預期線路性能的第一近似值。下面,我們將介紹這一研究的現狀和取得的認識。

元素金屬

根據第二章和第三章的討論,提出了以下三種材料特性,作為按比例互聯中金屬預期整體性能的代用指標:

(i) 體積電阻率 ρ0

(ii)電荷載流子的平均自由路徑 λ 或體電阻率與電荷載流子平均自由路徑的乘積 ρ0 ×λ

(iii) 內聚能或熔化溫度

根據第二章的討論,前兩個代用參數代表了小尺寸下潛在的低電阻率。第三個參數可視為電遷移硬度和無障礙可靠性的代用參數,因為一般來說,難熔金屬的性能會更好(見第 III 章)。第一個代用參數 (i) 可從文獻中獲得。ρ0的第一原理計算是可能的,但非常耗費資源,因此不能用於篩選廣泛的金屬。與此相反,ρ0 × λ(或等效張量的份量)可以比較容易地從原子彈初始計算中獲得,詳見第 II 章 C )。第三個替代值可以從文獻(熔點)或計算(內聚能)中獲得。通常情況下,熔點和內聚能之間具有良好的相關性(見圖 13a)159,160,因此它們可以互換使用。在實踐中,體積電阻率與平均自由路徑 ρ0 ×λ 的乘積被用作金屬的優劣值。然而,ρ0 ×λ 不應在不考慮代理 (i) 即體電阻率的情況下單獨使用。雖然這對於元素金屬來說很簡單,但對於二元和三元金屬來說可能會帶來問題,因為對於這些金屬,即使是基賓特性的瞭解也很有限,這將在下文中討論。

圖 13. (a) 各種元素的計算內聚能與熔化溫度的關係。(b) 對於電阻率低於 20 µΩcm 的各種元素金屬,根據計算的 ρ0 ×λ 乘積與實驗電阻率 ρ0 的關係推導出的平均自由路徑 λ。銅的位置突出顯示,以供參考。虛線表示 Cu 的 ρ0 ×λ 乘積的預期趨勢,即 ρ0 ×λ = 6.8×10-16 Ωm。

圖 14. 定性電阻率比例說明。平均自由路徑 λ 較小的其他金屬在較小的尺寸(如薄膜厚度)上顯示出與銅相似或更低的電阻率。

圖 14. 定性電阻率比例說明。平均自由路徑 λ 較小的其他金屬在較小的尺寸(如薄膜厚度)上顯示出與銅相似或更低的電阻率。單獨使用 ρ0 ×λ 值的主要問題在於 ρ0 和 λ 是相互關聯的,因為平均自由路徑短(弛豫時間短)會導致電阻率大(參見公式 (3))。圖 13b 展示了從 ρ0 × λ 乘積推導出的許多元素金屬的平均自由路徑與體積電阻率的對比。如圖 14 所示,對於銅來說,短 λ 確實會導致電阻率的厚度依賴性減弱,從而導致電阻率交叉。不過,即使對於恒定的 ρ0λ 乘積,替代金屬的較低體電阻率 ρ0 仍然是有益的,因為與具有較大 ρ0 的金屬相比,它通常會導致在較大厚度上與銅的交叉(圖 14)。雖然具有最小 λ 的金屬可能最終顯示出最低的電阻率,但交叉可能發生在與實際互連應用不太相關的尺寸上。

上述近似值可用於元素週期表中的所有金屬元素。以銅的 ρ0×λ (6.8 × 10-16 Ωm)、10 µΩcm 的體積電阻率和銅的熔點 (1358 K) 作為臨界值,可以確定表 II 中最吉祥的金屬元素,並以銅的特性作為參考。表 II 中列出了最吉祥的金屬元素,並以銅的特性作為參考。列表中包含幾種過渡金屬,包括幾種鉑族金屬,如 Ru、Rh 和 Ir。

表 II. 未來替代金屬以及作為參考的銅的特性:晶體結構、體積電阻率、計算得出的 ρ0×λ 優越性(見第二章 C 節)、推導出的平均自由路徑 λ、熔化溫度和計算得出的內聚能。

由於有前景的元素數量較少,因此都可以按照圖 3 中的工作流程進行薄膜實驗研究。圖 15 顯示了各種元素金屬薄膜電阻率的厚度依賴性。正如預期的那樣,由於平均自由路徑較長,銅的電阻率隨著厚度的減小而迅速增大,尤其是薄膜厚度低於 10 納米時。相比之下,許多其他元素金屬的電阻率增長要弱得多,根據金屬的不同,在厚度低於 5 至 10 納米時,薄膜電阻率與之相當,甚至更低。尤其是幾種鉑族金屬,如 Rh、Ir 和 Ru,顯示出較低的電阻率,這使得這些金屬在未來的互連應用中可能極具吸引力。電阻率建模70 發現,與銅相比,薄膜厚度依賴性較弱,最終薄膜電阻較低,這與作為關鍵參數的平均自由路徑較短有關。

圖 15. 幾種潛在替代金屬的薄膜電阻率與金屬疊層(薄膜)厚度的關係。有關鉑族數據,請參見參考文獻 70 和 163。

圖 15. 幾種潛在替代金屬的薄膜電阻率與金屬疊層(薄膜)厚度的關係。有關鉑族數據,請參見參考文獻 70 和 163。另一種值得關注的潛在金屬是鉬,它的薄膜電阻略高,但在互連集成方面具有多種優勢,而且成本比昂貴的鉑族金屬低得多。因此,鉬也被視為邏輯和存儲器互連應用的候選材料。

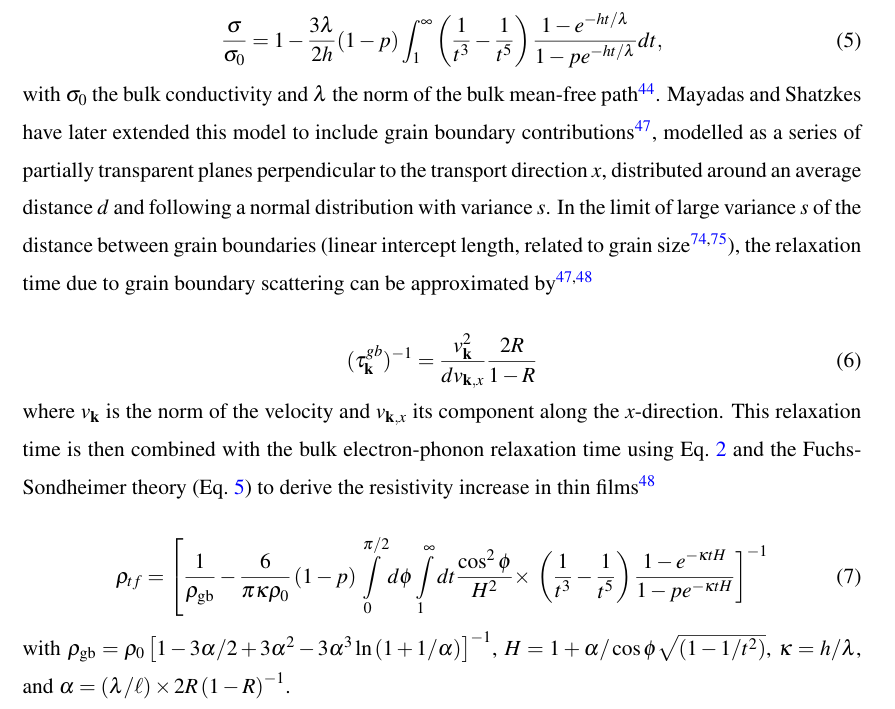

圖 16 中的結果表明,與最先進的銅大馬士革互連器件相比,銥互連器件的電阻率縮放效果更好,而 Ru 和 Co(在較小程度上)在足夠窄的線路上顯示出相似的電阻率。這些結果證實了薄膜結果,因此這些材料具有替代銅用於互連金屬化的潛力。請注意,儘管電阻率相當接近,但由於 Ru 的導電體積更大,因此在無阻擋層和襯墊的情況下,其線路電阻比 Cu 高得多。這將在第五章中進一步討論。

圖 16. Co 和 Ru 金屬化薄膜在沉積時的電阻率數據;Ir 和附加 Ru 的數據則是在 420◦C 進行沉積後退火後的數據。圖中顯示了銅雙大馬士革金屬化的參考線。

除了對薄膜和納米線電阻率進行評估外,還將一些選定的替代金屬集成到按比例放大的互連線路中,以研究其可靠性,特別是對阻擋層的需求。目前已獲得 Co、Ru 和 Mo 的具體結果。

在具有超薄低κ 薄膜的先進技術節點中,事實表明,保持疏水界面和連續厚的阻擋層對最大限度地降低金屬漂移風險至關重要,這對先進互連中鈷金屬化的集成性和可擴展性提出了重大挑戰。相比之下,鉬已被證明是一種很有前途的無屏障集成替代材料,無需在二氧化矽、有機矽玻璃或 SiCO 介電薄膜上形成附著層或屏障。這一結果已被多項研究證實。

Ru 是銅的第二種潛在無屏障替代材料。由於 Ru 具有較高的內聚能和出色的抗氧化性,因此可以在無阻擋層的情況下進行集成,儘管可能需要一個較薄的附著促進層。進一步的研究證實,當 Ru 與 0.3 nm 的 TiN 附著層集成時,Ru 的可靠性不會受到影響,沒有發現金屬漂移的跡象。此外,根據大馬士革 TDDB 結果,Ru 與緻密的低κ電介質(κ = 3.0)結合後,壽命可達 10 年。

此外,Mo 和 Ru 互連器件都具有出色的電遷移性能。圖 17 顯示了鉬互連器件電遷移測試的一個示例。

圖 17. (a) Mo-Ru 混合互連器件在 330◦C 和電流密度 J = 5 MA/cm2 > 600 小時條件下的電遷移測量結果,顯示沒有出現故障。(b) 顯示了測試結構的橫截面 TEM 圖像。轉載自參考文獻.

圖 18. Ru 互連中電遷移故障的透射電子顯微照片,顯示 (a) 晶界空洞和 (b) 介電界面空洞。轉載自參考文獻 184.

圖 18. Ru 互連中電遷移故障的透射電子顯微照片,顯示 (a) 晶界空洞和 (b) 介電界面空洞。轉載自參考文獻 184.此外,在高電流密度(J > 30 MA/cm2)條件下,試圖誘導無柵 21 nm 金屬間距 Ru 互聯線發生電磁故障,但未獲成功,這證實了 Ru 具有出色的抗電磁性能。182 在同一研究中,還使用無柵 Ru 互聯線在更高電流(150-200 MA/cm2)條件下進行了大量研究,這將誘發高自熱(∼ 260◦C)。只有在這些極端條件下,晶界和介電界面才會形成空隙(圖 18)。此外,Beyne 等人183 通過低頻噪聲測量研究了無阻擋層和粗糙表面的縮放 Ru 線,發現金屬/電介質界面成為主要的擴散路徑。

按照圖 3 的工作流程對元素金屬進行建模和實驗篩選的結果彙總於表 II。表 II 總結了按照圖 3 工作流程對元素金屬進行建模和實驗篩選的結果。我們發現六種元素金屬具有先進互連金屬化的潛在意義:鉑族金屬 Rh、Ru 和 Ir,以及過渡金屬 Ni、Co 和 Mo。雖然商用 CMOS 電路的局部互連中已經集成了 Co 173-175,但 Mo 和 Ru 因其即使在無阻擋層的情況下也具有高可靠性,在最終規模的線路和通孔中引起了極大的興趣。目前,結合氣隙的無阻擋 Ru 金屬化似乎是間距低於 20 納米的互連繫統中的佼佼者,而 Mo 則是研究最深入的替代品。

石墨烯和石墨烯-金屬混合金屬化

然而,純石墨烯是電荷載流子密度較低的半金屬,由於具有較高的薄層電阻,這嚴重阻礙了石墨烯在互連器件中的直接應用。最近,通過石墨烯與 FeCl3 的插層,電阻率值與銅相當(甚至更低)。插層過程保留了石墨烯的狄拉克錐,同時允許調節費米級,從而產生電荷載流子。然而,即使是高摻雜的插層石墨烯,在與金屬通孔共同集成時,接觸電阻仍然是一個挑戰。不同的 n 型插層種類可能會帶來潛在的改進,但要證明插層多層石墨烯能成功集成到按比例的互連器件中,還需要做更多的工作。

除插層石墨烯互連外,還研究了石墨烯-金屬混合復合金屬化方案。例如,對多層石墨烯封籃的 Ru 薄膜進行的評估顯示,與未封籃的 Ru 薄膜相比,片電阻和有效電阻率降低了約 10-20%(見圖 19b)。這與費米級降低 0.5 eV 有關,可能是通過 Ru 的電荷轉移導致了石墨烯的 p 型摻雜。在銅/石墨烯混合金屬化方案中也觀察到類似的片電阻和線電阻降低現象。雖然許多實驗都集中在包括單層石墨烯在內的混合材料上,但雙層或多層石墨烯可能會進一步降低電阻,儘管電荷屏蔽和層間電阻可能會限制額外的好處。

圖 19. (a) FeCl3 插層石墨烯的橫截面透射電子顯微鏡照片和 EDS 化學圖譜。轉載自參考文獻 198. (b) 不同 Ru 厚度的裸 Ru 和石墨烯封層 Ru 電阻率測量結果。轉載自文獻 200。

除了這些薄膜研究之外,石墨烯-金屬混合復合材料的集成還面臨著一些挑戰。沉積高質量石墨烯所需的沉積溫度通常高於互聯處理的熱預算(約 400◦C),因此需要開發無缺陷石墨烯的低溫工藝204 。此外,在集成時,例如在金屬圖案化方案中,石墨烯最好選擇性地沉積在圖案化互聯線路的側壁上,以避免相鄰線路之間的短路。另外,還研究了將石墨烯集成到大馬士革互連器件中205 的方法,從而獲得了巨大的電子遷移優勢。然而,未來的研究還需要證實這種混合方案在實際規模互連器件中的優勢。

二元金屬間化合物

上述對元素金屬的分析應被視為詳盡無遺,因為沒有一種潛在的金屬尚未得到評估。因此,為了進一步拓寬材料範圍,最近對化合物金屬進行了探索。在二元化合物金屬中,只有有序金屬表現出較低的體積電阻率(見第 II 章 B 節)。相比之下,無序化合物(合金)由於合金散射貢獻大,通常具有較大的電阻率。然而,對於有序金屬間化合物而言,在較窄的成分範圍內,實驗觀察到許多系統都具有較低的電阻率。圖 6 顯示了金-銅系統的一個眾所周知的例子,其中包括金屬間化合物 AuCu3 和 AuCu。圖中顯示,這些金屬間化合物的電阻率可能遠低於同一材料體系中無規合金的電阻率,甚至與組成元素金屬的電阻率相當。

對於二元金屬間化合物的基準和下選,第 IV 章 A 節中討論的元素金屬代用指標同樣適用。然而,由於潛在金屬間化合物的數量巨大,而且對其中許多化合物的瞭解有限,因此無法進行與元素金屬類似的全面基準測試和降序選擇。不過,正如第二章 C 節所概述的那樣,ρ0 ×λ 的優越性可以通過 ab initio 計算得到。熔點可從文獻(如二元相圖)中獲得。如果不知道熔點,則可以計算內聚能。Ab initio 篩選工作發現了大量具有低 ρ0 ×λ 產物且內聚能大於 Cu 的二元金屬間化合物(圖 20),但只有少數金屬間化合物的性能優於 Ru。不過,金屬間化合物的一個主要問題是,在許多情況下,體電阻率 ρ0 還沒有報告。因此,無法像元素金屬那樣直接進行類似的全面下選。

最有前途的材料包括 NiAl、AlCu、Al2Cu、AlRu 和 Al3Sc。最有前途的材料包括 NiAl、AlCu、Al2Cu、AlRu 和 Al3Sc。最有前途的材料包括 NiAl、AlCu、Al2Cu、AlRu 和 Al3Sc。表 III 總結了這些鋁化物金屬間化合物的特性,並將其與表 II 中有前途的元素金屬進行了比較。實驗證明,這些鋁化物的薄膜電阻率較低,儘管大多是相對較厚的薄膜 ≫ 10 納米。

通過在 420°C 高溫下沉積鎳鋁,並在原位添加矽帽以避免表面氧化,可進一步降低電阻率,在此條件下,22 納米厚薄膜的電阻率為 18 µΩcm。通過將背稀化實驗與外延相結合,可以進一步優化較小厚度的 NiAl 電阻率,從而使 Ge (100) 上 7.7 納米的外延 NiAl 電阻率低至 11.5 µΩcm。

圖 20. 二元金屬間化合物的 Ab initio 篩選:計算的 ρ0 × λ 乘積與計算的內聚能對比。圖中標出了幾種鋁基金屬間化合物,根據文中提到的篩選程序,這些金屬間化合物很有希望。

在這些條件下,22 nm 厚的薄膜電阻率為 18 µΩcm。通過將back-thinning 實驗與外延相結合,可以進一步優化較小厚度鎳鋁的電阻率,從而使 Ge (100) 上外延鎳鋁在 7.7 nm 時的電阻率低至 11.5 µΩcm。

厚度在 10 納米以上的 AlCu 和 Al2Cu 薄膜的電阻率低於 20 µΩcm,厚度在 30 納米左右的薄膜的電阻率低於 10 µΩcm。在薄膜厚度為 10 nm 及以上時,Al2Cu 的電阻率低於 Ru,而在研究的整個厚度範圍(5 至 30 nm)內,AlCu 和 Al2Cu 的電阻率均優於 Mo。在 8 納米以下,這兩種化合物也顯示出與 TaN/Cu/TaN 相似的電阻率。此外,Al2Cu 在 TDDB、EM 和 BTS 中表現出優異的間隙填充性能和良好的可靠性,但要證實 AlCu 和 Al2Cu 在高級高可靠性互連中的應用前景,還需要進一步的工作。

另據報導,24 納米 Al3Sc 薄膜在 500°C 沉積後退火後的電阻率為 12.6 µΩcm。電阻率受到晶界散射和點缺陷(無序)散射的共同限制,看來很難進一步提高。AlRu 也被列為替代銅的潛在候選材料,儘管迄今為止實驗電阻率仍然很高。作為替代金屬的潛在金屬間化合物的特性(包括作為參考的銅):晶體結構、體積電阻率、計算的 ρ0 × λ 優越性(見第 II 章 C 節)、推導的平均自由路徑 λ、熔化溫度和計算的內聚能。請注意,AlCu 和 Al2Cu 在 850 K 和 900 K 之間顯示出向不同高溫相的轉變,而不是向液相的轉變。

與本文討論的其他鋁相比。

就 Cu2Mg 而言,據報導,5 nm厚的薄膜電阻率為 25.5 µΩcm,通過濺射回流具有良好的間隙填充性能。然而,由於 Cu2Mg 和 SiO2 之間的界面反應,在底層 SiO2 層中形成了很厚的 MgO 層。因此,將 Cu2Mg 集成到低電阻線路所需的(接近)零界面形成的按比例互聯電路中是值得懷疑的。

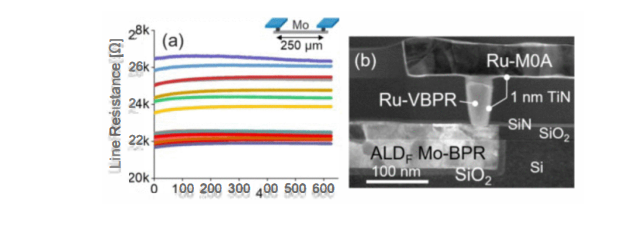

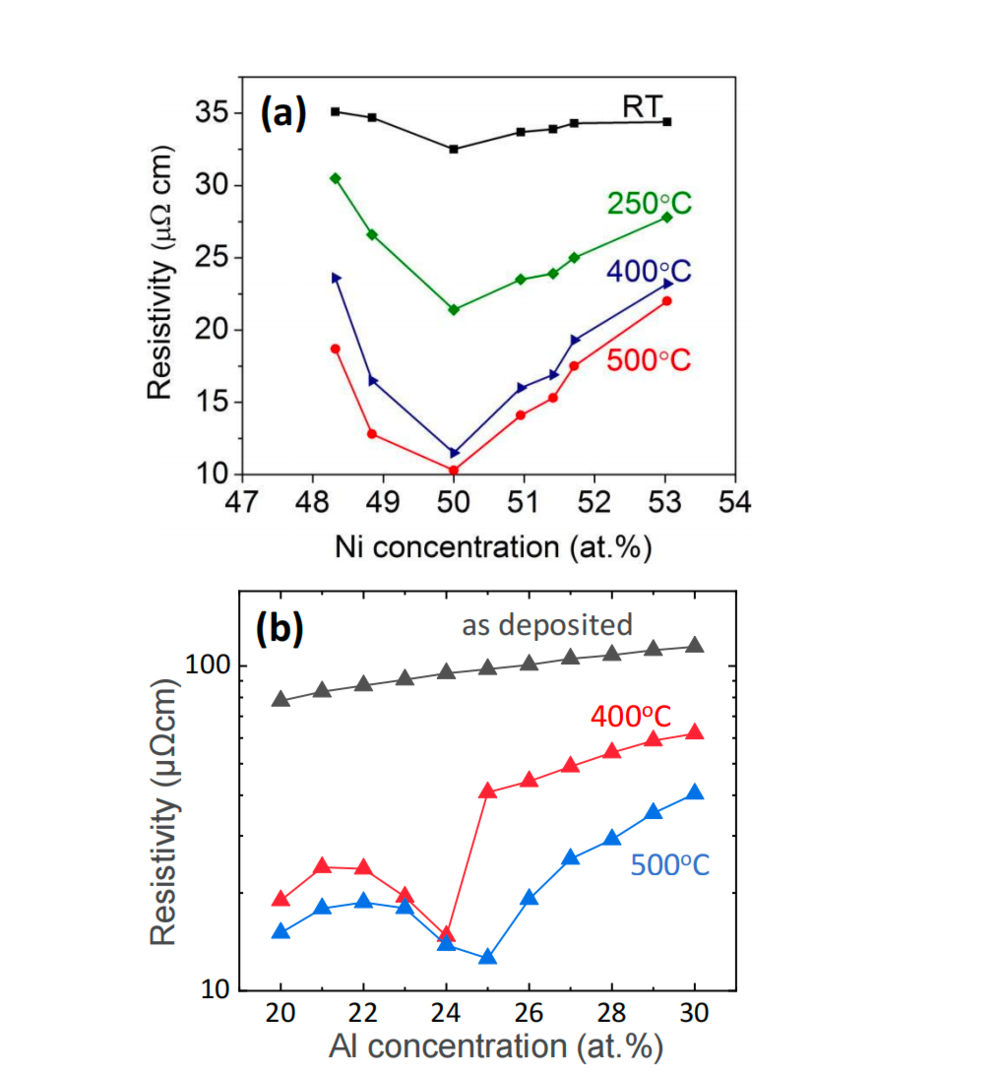

與元素金屬相比,二元金屬間化合物還面臨多種挑戰,如結晶有序性和減少點缺陷的需要、成分及其均勻性的控制、次生相的形成、團聚、(界面)反應性或非馳豫表面氧化,如圖 21 所示。一個主要挑戰是控制二元金屬間化合物的成分,如 Al1-xNix 和 AlxSc1-x 系統所示。如圖 22 所示,AlxNi1-x 的電阻率在化學成分為 Al0.50Ni0.50 時急劇減小(圖 22a)。圖 22b 顯示了 AlxSc1-x 的類似觀察結果。

根據第二章 B 節的討論,電阻率的增加可以理解為非化學計量點缺陷的產生,它導致了強烈的無序散射。實驗結果表明,要獲得低而均勻的電阻率,需要將成分控制在(優於)1% 的水平,而這在大批量生產中是具有挑戰性的。我們還注意到,在圖 22 中的兩種情況下,只有在沉積後高溫退火後才能觀察到低電阻率,這可歸因於熱激活有序(點缺陷減少)和晶粒生長。因此,需要仔細考慮這些退火步驟與器件加工流程熱預算的兼容性。

圖 21. 金屬間化合物面臨的共同挑戰

圖 21. 金屬間化合物面臨的共同挑戰

圖 22. (a) Al1-xNix 的電阻率與鎳濃度的關係。轉載自參考文獻 211. (b) AlxSc1-x 的電阻率與 Al 濃度的關係。

作為與二元金屬間化合物有關的其他挑戰的一個例子,我們展示了圖 23 中沉積的鎳鋁 薄膜在空氣中暴露後的橫截面 TEM 圖像和相關的 EDS 化學分析。化學分析結果表明存在原生表面氧化物,但其化學計量(近乎純 Al2O3)與薄膜主體不同。這可以用元素特異性表面過程來解釋,例如製約原生氧化物形成的金屬外擴散。

儘管具體的氧化物成分取決於材料系統,但我們發現鋁金屬間化合物具有這種相對普遍的特徵。 因此,在沉積後,也可能在圖案化後,這種(鋁)金屬間化合物最終可能需要原位表面鈍化步驟才能集成到按比例互連器件中。

圖 23. 30nm 厚的鎳鋁薄膜(二氧化矽/矽上)經空氣曝光後的高角度環形暗場 TEM 圖像以及 O、Al 和 Ni EDS 圖。EDS 圖像顯示存在 AlOx 表面氧化物。

三元化合物

除了二元金屬間化合物,人們還討論了幾種用於高級互連金屬化的三元化合物。對於三元化合物,由於潛在的金屬間化合物數量巨大,對其特性的瞭解非常有限,因此無法按照元素甚至二元金屬間化合物的方法進行系統篩選。因此,迄今為止的研究僅限於特定的材料類別。最近,MAX 相尤其引起了人們的興趣。MAX 相是層狀六方碳化物或氮化物金屬陶瓷,一般成分為 Mn+1AXn(圖 24a),其中 1 ≤ n ≤ 3,M 為(早期)過渡金屬,A 為 A 族元素,X 為 C 或 N。一些 MAX 化合物,如 Cr2AlC 和 V2AlC,顯示出低於 10 µΩcm 的面內室溫電阻率(圖 24b)。一項非比篩選工作發現了幾種 MAX 相的低ρ0 × λ 產物(見第二章 C 節),證實了它們在按比例互連金屬化方面的潛力。

圖 24. (a) 1 ≤ n ≤ 3 的 Mn+1AXn 結構,M 為(早期)過渡金屬,A 為 A 族元素,X 為 C 或 N,(b) Cr2AlC 和 V2AlC 單晶的面內電阻率隨溫度的變化。轉載自參考文獻 233. (c) 鉑鈷氧化物的結構

另一種具有潛在意義的材料系統是二化石氧化物,尤其是鈀鈷氧化物或鉑鈷氧化物。這些層狀六方化合物(見圖 24c)顯示出超低的體電阻率,與鋁相當,但平均自由通路也較長。

一般來說,三元化合物與二元化合物面臨著同樣的挑戰,上述關於成分控制等方面的討論預計也適用於此。此外,MAX 和 delafossite 復合物都是(強)各向異性導體,僅在平面方向上電阻率較低。雖然這也有好處,可以抑制頂面或界面的表面散射(見第 II 章 A 3 節),但薄膜的晶體學取向變得至關重要,必須實現沒有錯向晶粒的完全(001)紋理薄膜。因此,要驗證這些材料類別的潛力,還需要更多的實驗驗證。

超越二元和三元金屬間化合物:一維金屬和拓撲韋爾半金屬

如第二章 A 節所述,各向異性導電性和尺寸減小可以抑製表面散射。因此,一維導體被提議作為最終的互連導體,因為在這種情況下,互連線上下表面和側壁的散射都能被抑制。這與二維層狀系統(MAX、delafossite 氧化物)形成鮮明對比,後者在兩個方向上導電性良好,而在第三個正交方向上導電性較差。

與第二章 C 節中介紹的 ρ0 ×λ 張量類似,可以定義納米線的優越性,其中包括表面散射抑制的影響。具有潛在意義的一維金屬包括二元六方金屬間化合物(如 CoSn、OsRu)、正交金屬間化合物(如 VPt2、MoNi2)和三元硼化物(如 YCo3B2)。需要指出的是,目前還沒有關於此類材料的薄膜研究結果明確顯示其表面散射的抑製作用。此外,要集成到互連器件中,需要與互連線方向一致的高電導率單晶體。目前,還沒有製造這種互連器件的途徑。因此,要證明這種材料的潛力,還有很多工作要做。

此外,拓撲半金屬元素既包含 Weyl 半金屬元素,也包含作為子群的多折射鐵氧體半金屬元素,作為遠距離技術節點的潛在互聯材料,最近也引起了一些關注。Weyl半金屬具有獨特的電子結構,其特點是線性帶散佈和退化(Weyl)節點。特別是,它們具有高導電率表面態,這些表面態在拓撲上受到保護,並對無序狀態具有魯棒性。Weyl 半金屬的例子包括 TaAs、TaP、NbAs、MoP 或 NbP。

對於拓撲半金屬 NbAs,實驗表明有效電導率確實會隨著橫截面積的減小而增加,不過還需要進一步努力在互連相關結構中驗證這些觀察結果。與一維金屬類似,拓撲半金屬需要單晶(外延)導線。此外,基於拓撲半金屬的互聯可靠性尚不清楚,需要進一步的基礎研究才能實現隨尺寸線性擴展的互聯。

五、納米級互連線路的線路電阻建模

圖 16 中的電阻率趨勢可用於設計互聯線路電阻的校準模型,並以銅線電阻預測為基準。根據圖 16 中的數據,最近報告了一種適用於 Ru 和 Ir 互連的簡單幾何模型,其寬度為 w,高度為 h = w × AR,縱橫比為 AR。為了獲得無障礙線路電阻趨勢與線路寬度 w 的關係,我們從圖 16 中 Ru 經過 420◦C 沉積後退火的數據中提取了電阻率趨勢線與橫截面積的關係。Ru 金屬化方案還包括 0.3 nm 厚的粘附襯墊。

圖 25 顯示了 AR = 3(圖 25a)和 AR = 5(圖 25b)時,Ru 和 Cu 在不同擴散阻擋層和襯墊層組合厚度下的預測線路電阻。例如,模型顯示,在線寬為 w = 8 nm、縱橫比為 AR = 3、阻擋層和襯墊層總厚度為 2 nm 的情況下,Ru 互連線的線電阻比 Cu 的線電阻提高了約 3 倍。此外,電阻模型還有助於詳細瞭解銅基和 Ru 基互連器件之間線路電阻交叉的根源。

對 Ru 和 Cu 電阻率的定量比較(見圖 16)表明,與 Cu 相比,Ru 的線路電阻優勢並非源於電阻率的大幅降低,而主要源於當 Cu 可靠性所必需的阻擋層和線路層被更薄的 Ru 粘附層取代時,導體體積的增加。儘管如此,電阻率縮放仍然起著重要作用。由於銅的體積電阻率非常低,無勢壘替代金屬的電阻率縮放不足必然會導致小尺寸的高電阻率,這將抵消導體體積增大帶來的潛在收益。因此,無勢壘金屬化和有利的電阻率縮放必須相輔相成,才能實現低線路電阻。

雖然 AR 與材料的內在特性無關,但它在很大程度上取決於集成路線所能達到的效果。對於銅雙層大馬士革(圖 2),由於採用了銅填充工藝,AR 值僅限於 2-3。然而,其他集成方案,如半大馬士革集成(見圖 26)–基於大馬士革填充和直接金屬蝕刻線圖案化的組合–可以通過其他金屬實現。

雖然銅蝕刻按比例繪製的高 AR 線仍然極具挑戰性,但 Ru 和 Mo 反應離子蝕刻技術已經成熟。如圖 25b 所示,將縱橫比增加到 AR = 5 時,在 w = 8 nm 時,Ru 比 Cu(AR = 2 時)的線路電阻提高了 5 倍,阻擋層/線路的總厚度增加了 2 nm。

圖 25. 以 Ru28 和 Cu 的校準模型為參考,在縱橫比為 (a) AR = 3 和 (b) AR = 5 時的預測線電阻。Ru 模型包括 0.3 nm 厚的粘附襯墊,而 Cu 趨勢線則分別顯示了 2 nm 和 3 nm 厚的聚合阻擋層和襯墊。

圖 26. 半級聯互連集成路線示意圖;a) 通孔蝕刻;b) 通孔的金屬填充,然後是金屬過填充,c) 使用過填充金屬層進行線路蝕刻。

六、工藝整合挑戰的物質方面

最終,將替代金屬集成到按比例互連中需要開發單元工藝步驟和圖 3 中替代金屬工作流程最後一步中的金屬化(圖案化)工藝模塊。雖然對現有工藝技術和賸餘差距的詳細回顧超出了本教程的範圍,但我們在此簡要介紹了在開發按比例互連線製造過程中變得越來越重要的材料特性。

附著力和應力

互連金屬化的一個關鍵特性是與周圍(低κ)電介質的附著力。金屬-電介質界面通常很薄弱,比金屬-金屬或金屬-電介質界面薄弱得多,這可能導致金屬薄膜脫層和災難性後果。一般來說,貴金屬與電介質的附著力要比賤金屬弱得多,這是因為界面結合力較弱。由於與周圍電介質或金屬之間的範德華相互作用較弱,高質量石墨烯通常也具有較弱的附著力。

通過在主要金屬(如貴金屬)和周圍電介質之間引入附著襯墊,可以改善附著力。然而,與擴散屏障的情況一樣,這種粘附屏障會佔用線路和通孔的體積,而對導電性的潛在貢獻卻很小。101 因此,鉬金屬化可以做到真正的無屏障和無襯墊。相比之下,惰性金屬 Ru 與電介質的附著力不足,需要附著襯墊(如 TiN 或 TaN)。這表明,即使是非閉合薄膜也可以用作粘附襯墊,並表明這些襯墊可以比擴散屏障更好地擴展。不過,即使是 Ir 和 Rh 等惰性金屬也可能需要進一步關注,以避免出現粘附力弱和分層現象。

薄膜(或整個疊層)中的高內置應力也會導致分層,從而進一步削弱界面。此外,填充過程中的高壓應力和毛細力也會導致納米結構變形,例如線擺動。應力並非金屬的固有屬性,而主要由沉積方法決定。尤其是 PVD 薄膜在沉積後會顯示出很高(通常是拉伸)的應力。這可能與成核和生長的最初階段孤島凝聚過程中產生的應力有關,儘管整體行為可能很複雜。例如,沉積後的 PVD Mo 薄膜顯示出高達 1500 兆帕的內置拉伸應力,這與薄膜厚度有關。然而,沉積後的退火和相關的晶粒生長強烈地改變了應力,甚至導致在一定溫度窗口內冷卻後產生壓應力。

抗氧化性

在互連圖形化過程中,一些金屬表面可能會暴露在空氣(或其他反應性環境)中,因此 化學惰性,特別是抗氧化性問題至關重要。即使是自我限制的表面氧化過程也會產生厚度約為 2 nm 的原生表面氧化物(實際上是電絕緣),通常會消耗約 1 nm 的金屬。很明顯,貴金屬的化學性質比賤金屬要強得多。雖然這也會導致較弱的附著力,並帶來不同的相關挑戰,但這使得貴金屬更容易集成到互連工藝流程中。

復合金屬的情況更為複雜。正如在第四章C節中討論的 NiAl(見圖 23),二元金屬的表面氧化物可能是非共沸的,甚至在緊靠表面氧化物下面的區域也會導致成分改變。209,220 因此,在這種材料系統中,按比例互連線的成分控制非常具有挑戰性,需要避免表面氧化。雖然這些問題原則上可以通過原位圖案化和鈍化或封籃來解決,但這會大大增加工藝的複雜性,因此在金屬選擇過程中應加以考慮。

圖 27. 通過 Rh 電鍍填充的 < 40 nm 寬線的橫截面 TEM 圖像。

圖 27. 通過 Rh 電鍍填充的 < 40 nm 寬線的橫截面 TEM 圖像。工藝技術

如上所述,對銅和替代金屬集成工藝技術現狀的詳細回顧超出了本教程的範圍。不過,從總體上看,每種互連集成路線都需要開發關鍵的單元工藝步驟,以製造一定規模的互連器件。雙大馬士革(圖 2)和半大馬士革集成路線(圖 26)都需要採用電鍍或化學氣相沉積的金屬溝槽和通孔填充工藝。

在雙大馬士革集成路線中,線路分離需要一個化學機械拋光(CMP)步驟,而在半大馬士革集成路線中,線路是通過活性離子蝕刻(RIE)的直接金屬蝕刻形成的。對於銅來說,CMP 工藝具有極佳的工藝控制能力,而 RIE 仍然具有很高的挑戰性。因此,銅非常適合雙級聯集成,而半級聯集成則不太適合。

對於替代金屬而言,這意味著除了沉積工藝外,還必須具備具有所需特性和良好工藝控制的 CMP 和/或 RIE 工藝。例如,Rh 具有低電阻率和高熔點,具有很高的抗電遷移潛力。260 在限制附著襯厚度以避免導體體積減小的同時,附著工程仍面臨挑戰。Rh 可以電鍍,並已證明可以填充寬 < 40 nm 的線路和具有高縱橫比的通孔(圖 27)。

然而,雙層大馬士革集成需要 CMP,這對 Rh 來說還不成熟,需要高腐蝕性的磨料和氧化劑。因此,還沒有關於 Rh 的可製造 RIE 工藝的報導,這阻礙了半大馬士革集成方法的發展。因此,缺乏可製造的 CMP 和/或 RIE 工藝仍然是在商用 CMOS 電路中實現 Rh 金屬化潛力的主要障礙。

七、替代金屬的可持續性

傳統上,選擇替代互連金屬的標準主要側重於技術、物理和經濟屬性。不過,考慮到將可持續性方面(SAs)納入決策過程的重要性與日俱增,本節介紹了評估替代互連金屬可持續性的簡化框架。它包括七個可持續發展方面,並評估了當前和替代互連金屬(銅、鋁、鎳、釕、鈷、鉬、銥、銠)的實例。在採用生命週期方法以避免轉移環境負擔時,必須考慮替代互連金屬的整合方法。

瞭解集成過程中的材料和能源流對於衡量整體可持續性至關重要。雖然步驟較少的工藝通常會減少對環境的影響,但考慮集成過程中的能源需求也至關重要。本節將討論這些對全面評估至關重要的集成考慮因素。此外,本節還簡要概述了參考文獻中詳述的可持續性評估框架。

擬議的互聯金屬可持續發展評估框架分為七個可持續發展評估。每個 SA 至少有一個量化影響的指標。SA1 側重於供應風險,利用赫芬達爾-赫施文指數(HHI)估算市場集中度。表 IV 中的 HHI 值摘自參考文獻 表 IV 中的 HHI 值摘自參考文獻 265 和 266。SA2 涉及關鍵性和衝突,考慮了美國和歐盟關鍵原材料 (CRM) 列表中的金屬以及歐盟衝突礦物列表。SA3 深入研究金屬的循環性、 SA3 深入研究金屬循環性,評估集成電路製造工藝中的材料使用情況,並承認計算現場材料循環性指數 (CI)270 是一項挑戰。

SA4 通過全球升溫潛能值 (GWP)271 評估對氣候變化的影響,而 SA5 則重點關注缺水問題,採用 EF 3.1 方法272 評估上遊用水情況。SA6 通過非生物資源耗竭潛能值 (ADP) 來研究對自然資源的影響,SA7 則使用 EF 3.1 方法評估對人類健康的影響,如 “人類癌症和非癌症毒性 “和 “顆粒物”。這些指標共同為替代性互連金屬的可持續性提供了一個全面的視角。有關每個 SA 及其指標的更詳細解釋,請參見相關參考文獻。

表 IV 概述了所研究的互連金屬的可持續性表現,從細微處展示了七個擬議指標。可持續性影響(表 IV 中的 SA4-SA7)是根據生產 1 立方釐米金屬的 “從搖籃到柵極 “影響計算的。這種計算方法假定最終沉積的互連金屬層的體積與金屬無關。不過,應考慮達到所需最終沉積體積所需的體積比。

評估金屬沉積效率 ηdep 對於確定實際使用體積 Vu 至關重要。典型沉積工藝的 ηdep 值範圍在 1% 到 20% 之間,適用於基於化學氣相的沉積工藝275 ,但對於物理氣相工藝,ηdep 值可能要高得多。此外,減法集成方案會導致進一步的材料損耗,這取決於集成工藝的材料使用效率 ηint,並受互連金屬選擇的影響。相比之下,大馬士革集成方案需要在 CMP 之前沉積大量覆蓋層,這也會導致 ηint ≪1。Vu 可定義為:

其中,VIC 是製造互連(層)的體積,由互連尺寸以及特定電路的通孔和線路密度決定。

通過表 IV 中 SA4-SA7 的體積影響,可以更準確地評估互連金屬對特定可持續性方面 IXmet 的環境影響。

上述介紹簡要概述了替代互聯金屬的簡化可持續發展評估方法。擬議的七項可持續發展指標提供了一種全面的生命週期思維方法,可實現全面的可持續發展評估。對錶 IV 中的體積影響值進行定性分析,有助於工藝工程師確定權衡。表 IV 中的定性分析可幫助工藝工程師確定權衡取捨,並為開發先進互連應用的明智決策提供支持。 值得注意的是,Al、Ni、Co 和 Mo 在七項指標中至少有三項表現相對較好,而鉑族金屬(Ru、Ir 和 Rh)在七項指標中至少有六項表現相對較差。

進一步的分析包括將表 IV 中的體積影響乘以消耗的金屬總量。進一步的分析包括將表 IV 中的體積影響乘以實現固定功能所消耗的金屬總量,即固定的沉積金屬量。這包含了沉積和集成方法固有的材料使用效率。此外,建議應用歸一化或加權因子,根據具體情況(如公司特定的可持續發展目標、承擔財務風險的意願或特定地點的法規/材料可得性)確定可持續發展指標的優先次序。結合技術評估,這種簡化的可持續發展方法為決策者在選擇先進互連應用的替代金屬時擴展標準奠定了基礎。

八、總結和結論

如今,互連金屬間距的縮放已成為先進微電子芯片技術發展的關鍵重點。隨著晶體管間距的擴展達到物理極限,縮小最小金屬線間距已成為進一步縮小電路面積的主要策略。雖然通過堆疊可以提高晶體管密度,但這種方法也需要更緊密的金屬間距來防止互連擁塞,從而抵消了堆疊帶來的好處。

此外,互聯 RC 時延在很大程度上限制了 CMOS 電路的吞吐量,這在幾個技術節點上已經存在。為了控制 RC,必須優化金屬化的電阻 (R) 和電容 (C)。 要優化 R,就必須在線路和通孔中填充電阻率儘可能低、體積儘可能大(在給定間距下)的金屬,從而改進金屬化方案。優化 C 需要使用低κ電介質或在線路之間形成氣隙。不過,這方面的內容超出了本教程文章的範圍。

目前的銅基雙層金屬化方案於 1999 年推出,由於多種原因,這種方案正面臨越來越大的壓力。為了滿足可靠性標準,銅金屬化需要阻擋層,以防止銅原子漂移或擴散到周圍的電介質中,從而導致電介質擊穿。迄今為止,TaN 仍是標準的阻擋層材料。此外,為了滿足電遷移標準,還在銅和 TaN 阻擋層之間以及銅線頂部引入了鈷襯墊層(全方位鈷)。TaN 層和 Co 層在按比例互連器件中都佔據了相當大的體積分數,但對線路電導的貢獻卻相對較小。

然而,這些 TaN 隔層和 Co 內襯層的厚度不可能無限制地減少而不影響其功能。儘管我們一直在努力擴大厚度限制,但要達到 1 納米的綜合厚度仍具有很大的挑戰性。即便如此,在 10 nm 線寬的情況下,1 到 1.5 nm 的阻擋層和襯裡組合厚度也將佔據 20% 到 30% 的線體積,對線路電阻產生相當大的影響。此外,使用大馬士革工藝對如此窄的線路進行無空隙填充的難度越來越大,這表明銅雙大馬士革金屬化工藝很可能無法用於 20 納米以下的金屬間距。

在過去十年中,這些問題促使人們尋找銅(雙大馬士革)金屬化的替代品。鑒於互連的結構簡單,改進主要源於材料的選擇,這使得替代互連金屬化成為材料科學的一個引人入勝的領域。正如本問所示,尋找新型互連金屬需要考慮多種標準的綜合方法。雖然線路電阻是最關鍵的因素,但可靠性和熱方面也不容忽視。正如經校準的窄線模型(第五節)所示,低線路電阻要求導體金屬具有低電阻率和無屏障金屬化,以最大限度地增加導體金屬填充的可用體積。

因此,有前途的替代金屬必須滿足介電擊穿和電遷移標準,而無需屏障。其他重要的材料標準包括與周圍電介質的粘附性、內置應力和抗氧化性。此外,工藝就緒性和可持續性也不容忽視。

電阻和可靠性標準的結合促使人們關注難熔金屬–它們具有良好的可靠性,而且電荷載流子的平均自由路徑較短,從而促進了按比例尺寸的低電阻率。研究最初以元素金屬為中心,但最近已擴展到二元和三元金屬間化合物。在所有被研究的材料中,Ru 和 Mo 是迄今為止最有前途的。半導體行業正致力於開發必要的工藝技術,以便在不需要屏障的情況下將這些金屬集成到 10 納米以下的金屬線中。這些金屬良好的蝕刻性還開闢了其他集成途徑,如半二疊紀集成,這可能允許更高的高寬比鼠線性,進一步降低線路電阻。因此,這些金屬有望在未來十年內集成到未來技術節點的邏輯和存儲器件中。

其他有前途的導體材料包括插層石墨烯,從長遠來看,還包括拓撲材料,如韋爾半金屬。目前,所有這些方法,包括二元和三元金屬間化合物,都是以薄膜的形式進行研究的,它們在按比例導線中的行為仍是未知數。正如第 IV 章 C 節所述,與元素金屬相比,將這些材料集成到互連器件中的複雜性要高得多。這些材料的可製造工藝技術之路才剛剛開始。儘管如此,人們對如此廣泛的材料的興趣,以及未來可能出現的更多材料類別,表明該領域在未來許多年仍將是材料科學的一個令人著迷的領域。

參考鏈接:https://arxiv.org/abs/2406.09106

本文來自微信公眾號:半導體行業觀察,作者:imec