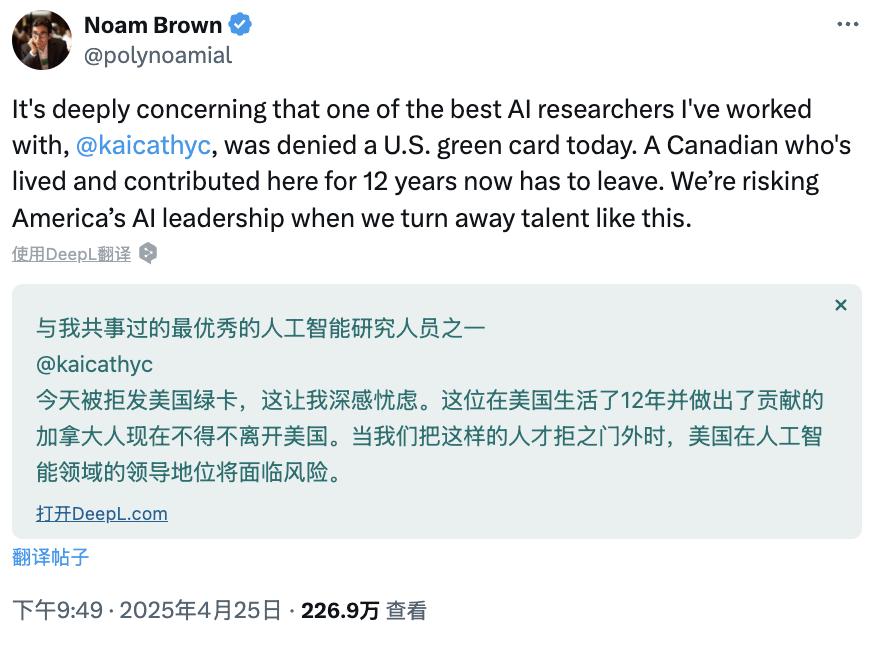

RISC-V驅動中國芯,打破高性能處理器的「不可能三角」

文 | 矽星聞

剛剛過去的三月底,國產RISC-V迎來破局時刻:知名芯片設計企業睿思芯科在深圳正式發佈中國首款全自研高性能RISC-V服務器處理器——靈羽處理器。

3月31日,睿思芯科在靈羽處理器發佈會現場舉辦用戶啟航儀式

3月31日,睿思芯科在靈羽處理器發佈會現場舉辦用戶啟航儀式服務器處理器的性能門檻極高,既在於算力、功耗、接口等維度的極致需求,還在於生態兼容性、穩定性、安全性的嚴苛要求,一向被視為國產處理器研發領域難以攀登的「珠穆朗瑪峰」。

作為挑戰X86、ARM的第三大指令集架構,由加州大學伯克利分校主導設計的RISC-V以開源、模塊化、可定製為核心特性,擺脫了傳統架構的授權束縛和地緣風險。從最初的AIoT、MCU等輕量級場景到如今的服務器處理器等高性能應用,RISC-V正成為全球計算架構變革中的關鍵變量,而睿思芯科則代表著難以忽視的中國力量。

睿思芯科創始人、董事會主席兼CEO譚章熹博士是RISC-V發明者David Patterson教授的關門弟子、也是唯一的中國大陸博士生。基於伯克利的先進方法,結合對RISC-V十數年的深入鑽研與實踐,譚章熹博士帶領團隊建立起一套快速迭代微架構、軟硬件一體設計工藝協同優化的完整技術體系。

憑藉此次發佈的「靈羽」處理器,睿思芯科真正在國產服務器處理器領域打破了高性能、CPU核心研發、SoC芯片研發三者難以兼得的「不可能三角」,首次將一款具備實用能力的高性能、高獨立性國產服務器處理器推向市場。

從伯克利實驗室到深圳,精簡指令集四十年傳承

精簡指令集(RISC)誕生於上世紀80年代,旨在以更簡潔高效的指令架構,提升芯片在面積、功耗受限場景下的執行效率。從MIPS、SPARC、PowerPC到ARM,RISC架構推動了計算從工作站、PC走向移動計算與智能終端,成為全球芯片架構演進的重要引擎。

睿思芯科董事會副主席容誌誠博士是這一浪潮的親曆者。他在紐約成長,24 歲獲得首項芯片設計專利,隨後在加州大學伯克利分校取得電子工程與計算機博士學位,師從「現代計算機架構之父」、2017 年圖靈獎得主 David Patterson 教授,深度參與了RISC-I與RISC-II兩代架構的演進。

容誌誠加入 Sun Microsystems後,創立首個 64 位 UltraSPARC 精簡指令集處理器團隊並擔任首席架構師,併成為 SPARCv9 64 位指令集架構國際標準的起草者之一。他於 1995 年獲得的關鍵芯片專利,是該領域全球首創,顯著提升了處理器高速緩衝存儲器的效率,被廣泛應用於之後多個處理器體系,成為微架構設計中的標誌性突破。而後,他出任Sun Microsystems亞洲首席技術官。

容誌誠博士,華胥基金創始管理合夥人,睿思芯科董事會副主席

容誌誠博士,華胥基金創始管理合夥人,睿思芯科董事會副主席彼時的 Sun 正值巔峰:1982 年成立、1986 年即上市,1993 年進入《財富》500 強,2001 年市值一度超過 2000 億美元,躋身全球頂級科技公司之列。作為最早將 RISC 商業化的公司,Sun 憑藉 SPARC 架構成功佔據高性能工作站與服務器市場,其技術路線成為後續精簡指令集架構的重要參考。

此後,容誌誠博士加入英特爾(Intel),擔任英特爾中國首席技術官,並於1998年創立了英特爾中國研發中心。其後,他先後擔任英特爾企業處理事業部首席技術官、英特爾通信產品事業部首席技術官。

在中美兩地,容誌誠博士持續推動軟硬件系統創新,見證了三代 RISC 架構的產業更迭,始終站在全球計算產業前沿,有超過60項專利應用於最前沿的微處理器和計算機制造技術中。

與此同時,在他曾求學與工作的伯克利校園,另一位年青人也走上了精簡指令集技術之路。

2005 年,譚章熹博士自清華大學畢業後赴伯克利深造,加入由 Patterson 教授主導的 RISC-V 項目組,成為其關門弟子、也是其唯一研究計算機指令架構的中國大陸博士生。他從項目早期便參與 RISC-V 指令集的設計、標準製定與驗證推廣,是第五代精簡指令集最早一批技術奠基者。

譚章熹博士,睿思芯科創始人、董事會主席、CEO

譚章熹博士,睿思芯科創始人、董事會主席、CEO從伯克利畢業後,譚博士曾加入Pure Storage公司,是其首位芯片設計工程和關鍵產品FlashBlade的最早主要設計工程師;2017年,他在矽谷創立了自動駕駛芯片公司OURS Technology,並在短時間內成功將公司出售給美國自動駕駛獨角獸Aurora,完成從學術研究到產業落地的閉環。

2018 年,他選擇回國創業,在深圳創辦睿思芯科,專注於RISC-V 芯片產品,並立下目標:「希望每一行處理器代碼都由中國人寫出來。」在他看來,芯片屬於工程科學,必須走出實驗室、走向產業,才能實現真正的工程迭代與長期突破。

一個是精簡指令集第一代架構的產業拓荒者,一個是第五代 RISC-V 的原生設計者,兩位跨越年代的「Patterson 弟子」彙聚一堂,試圖為中國芯片產業打造真正意義上的「架構原生、軟硬協同、自主可控」的計算核心。

這正是睿思芯科與靈羽處理器背後的起點——從伯克利實驗室到深圳高性能服務器,從 SPARC 到 RISC-V,從一個人的技術延續到一代人的工程體系,精簡指令集的故事,在中國迎來新的轉折點。

打破「不可能三角」,全自研服務器處理器推開自主可控之門

2025年3月底,睿思芯科發佈了中國首款全自研高性能RISC-V服務器處理器——靈羽。兩位師出同門、跨越代際的架構工程師,以RISC為線索,將精簡指令集四十年技術演化貫通,在中國構建起以RISC-V為核心的新一代高性能計算平台。

據悉,靈羽處理器專為大語言模型等高密度推理場景設計,性能指標已比肩Intel與AMD等主流服務器處理器。

性能及能效比方面,該芯片基於公司自研的CPU IP與NoC(片上網絡)IP,採用32核高性能通用CPU + 8核智算LPU的「一芯雙核」架構,實現了先進亂序執行、高速數據通路與Mesh互聯結構;同時通過軟硬件結合的設計-工藝協同優化,在產品工程、EDA工具鏈、物理設計與晶圓製造流程中實現創新,顯著提升運算中的能效比以及優化總體擁有成本(TCO)。

為適配計算密集型場景,靈羽在內存與I/O架構上也做出全面升級:支持DDR5高速內存、PCIe 5.0標準與CXL 2.0協議,提供高達8路互聯能力。這使其能夠滿足大模型時代多種新型計算需求,包括20盤以上NVMe全閃存儲服務器、8卡GPU直連、最高320核高密度算力、以及多達6張400Gbps高性能網卡等複雜部署環境。此外,靈羽還具備企業級RAS特性,滿足RISC-V服務器標準,內置專用管理核心並支持動態調節,保障高負載運行的穩定性,滿足企業級數據中心需求。

這意味著,從架構能力到軟硬協同,從性能指標到產業適配,睿思芯科首次實質性打破了國產服務器CPU領域長期存在的「不可能三角」:高性能、CPU核心研發、SoC芯片研發難以三者兼得的結構性難題。

此前,中國市場在中低端處理器領域已具備一定的CPU核心及SoC芯片研發能力,高性能處理器領域也有CPU核心IP成果,但在結合CPU核心及SoC芯片的系統級產品方面仍屬空白。

相比基於外購 IP 拚接構建系統的方式,完整 SoC芯片研發能實現計算核心、片上互聯、內存子系統到外設接口的全鏈路深度協同設計,實現各模塊間的最佳適配,更好地釋放多核架構潛力,有效提升處理器在智算中心等複雜負載下展現出更優的系統性能與穩定性。這也是實現真正高性能、可持續迭代能力的必經之路。

這一重要產品,展現了睿思芯科的核心優勢:基於CPU核心與NoC 結構的全面自研能力,通過軟硬件一體化設計的協同優化體系,能夠實現真正意義上的高性能、高自主、高完整度。

事實上,靈羽並非睿思芯科首次在高性能RISC-V處理器領域實現技術領先。在發佈靈羽之前,睿思芯科已通過多個差異化CPU核心IP產品持續積累核心優勢,為高性能架構技術基礎。

2022 年中發佈的V7 DSP,是全球首個將向量核引入專業音頻 DSP 領域的產品,已在國際頭部客戶中集成量產;2022 年底發佈的P600,則是業內首批商用支持 RVV 1.0 向量擴展的高性能處理器 IP,採用亂序多發射架構,支持 DDR5、PCIe Gen5 等高帶寬接口,已被用於多個數據中心場景。P600 架構中所採用的亂序執行、Mesh NoC、以及 SoC 級的性能調優機制,也正是靈羽處理器的重要技術基石。

靈羽處理器

靈羽處理器以這些自研 IP 為基礎,睿思芯科在靈羽處理器的研發過程中進一步實現了多核高併發架構、系統級優化的突破,在高併發、多任務等關鍵指標上完成產業級驗證,為全面自研、高能效的高性能服務器處理器提供了強有力的技術支撐。

從睿思芯科的產品路徑中不難看出,在RISC-V的開放體系下,企業可以真正參與架構演化,更能基於自主技術快速響應新需求,而非像X86或ARM體系那樣只能「買IP、等更新」。這種開放性,為中國芯片產業打開了一扇真正意義上的「自主可控」之門。

RISC-V驅動,第三代中國芯的破局時刻

睿思芯科能實現這一突破,根源在於伯克利方法論的落地實踐。

20世紀60年代以來,圍繞處理器的中國芯大致經歷了三代探索。第一代中國芯以「跟跑」為主,以手工設計為主,在缺乏EDA工具的年代完成了早期 32 位處理器的工程實現,更多是科研型突破;第二代嘗試「局部並跑」,在 2000 年後逐步引入自動化工具,嘗試構建自有指令集或基於 ARM 等架構開展開發,但由於軟硬件分離,生態始終無法真正打通,自主性受到製約。

正因此,第三代中國芯的核心挑戰,是如何真正做到「從架構出發」的原生能力構建。而譚章熹博士在睿思芯科實踐的,是發源於伯克利的一整套軟硬件協同演化的方法論,也是真正意義上的自研範式。

舉例而言,傳統ARM架構授權體系下,企業雖然可以買到IP,但微架構的方向完全由ARM公司壟斷。即使付出巨大研發投入,一旦ARM在新版本上更改規則,生態就可能斷裂,過去的努力也可能被清零。

而在RISC-V體系下,這樣的局限被徹底打破。中國企業可以在指令集架構基礎上,自主決定微架構演化方向,同時構建自有軟件棧,掌握真正的設計主權。

這才是所謂「自主可控」的核心——不僅是「是否用了國產IP」,而是「是否掌握了架構演進的主動權」。

具體到研發效率上,睿思芯科已將微架構迭代、工藝製程的研發週期相結合,每年推出一款旗艦芯片。在實際項目中,針對不同場景需求,從指令級設計到芯片流片,團隊都能實現快速響應。

這也意味著,睿思芯科不僅能在本次的服務器芯片上實現突破,也有能力在未來其他需求中快速開發合適的產品。

從某種意義上看,第三代中國芯的破局時刻,不在於一次產品發佈,而在於是否掌握了快速演化、構建生態、跨越週期的核心能力。

RISC-V不僅是一種技術選擇,更是一種國家層面的戰略路徑選擇。從歐洲、俄羅斯到印度,越來越多的國家已經將RISC-V視為實現技術獨立的基礎設施。2021 年,中國首次在「十四五」規劃中將「開源」明確寫入發展戰略,為 RISC-V 在本土的生態建設、技術突破與人才培養提供政策支撐。中國若能在這輪架構更替中佔據正選優勢,將有可能建立起屬於自己的全球影響力。

RISC-V生態啟航,推動芯片產業長線發展

推動芯片產業發展,不僅需要技術路線和單點突破,更需要系統性的生態構建,而睿思芯科已經在高性能領域完成廣泛生態佈局。

生態建設方面,隨著靈羽處理器的正式落地,睿思芯科也集結了包括聯想、長城、三諾等在內的眾多頭部OEM與解決方案企業,共同推動基於RISC-V架構的高性能服務器進入規模化部署階段。靈羽處理器已適配包括 openKylin、Fedora、Deepin 等國產與國際操作系統,全面支持主流數據庫、機器學習框架、虛擬化平台和容器化環境,具備大規模產業應用能力。

在關鍵器件方面,睿思芯科與江波龍共同研發基於靈羽的智能全閃存儲系統,並與星辰天合合作,構建了覆蓋雲邊協同、數據存儲與管理等多層級的系統生態。至今,靈羽處理器生態體系已彙聚超50家合作夥伴,涵蓋整機OEM、系統軟件、行業解決方案、EDA工具鏈等多個核心環節。

在這場以RISC-V為代表的全球架構遷移中,睿思芯科不僅是一家技術公司,具備打造擁有核心競爭力的產品能力,也正在成為連接方法論和生態體系的關鍵橋樑,通過與產業合作夥伴協同推進,為中國在 RISC-V 賽道構建起更紮實、具持續性的技術與生態基礎。